客服專線

close

-

聯絡電話

-

傳真號碼04-3602-9038

-

電子信箱

-

週一 ~ 週五08:30 ~ 18:00

-

週六08:30 ~ 17:00

-

星期例假日全休

臺中市西屯區環河路18號 (林酒店正對面,老虎城正後方)

網站操作

服務時間 : 週一 ~ 週五 08:30 ~ 18:00 週六 08:30 ~ 17:00 星期例假日全休消費滿 1400 免運費

標示價格均為 含稅價 TWD

lightbulb

快速了解產品優勢

help 這款 CH-JN1270 CPLD 高性能應用板最適合投入哪些硬體開發專案中?

本產品適合用於電機順序控制、系統配置管理、I/O 擴展及界面橋接等應用場景。其具備非易失性與即時上電特性,能有效取代成本較高的 FPGA 或複雜的標準邏輯元件,協助工程師在低功耗需求下完成高效率的數位邏輯控制設計。

help 哪些專業群體或教學機構最需要採購 CH-JN1270 高性能實驗板?

主要針對 STEM 教育機構、大學電子工程系所實習以及機電整合系統開發團隊。特別是需要進行邏輯電路教學實驗,或是在 B2B 專案中尋求低成本、多 I/O 解決方案的系統開發者,這款提供 144 支接腳的實驗板是理想的採購選擇。

help 與同級產品相比,CH-JN1270 在技術規格與硬體擴充上有何核心亮點?

核心搭載 ALTERA MAX II 晶片,提供多達 144 支 I/O 引腳並內建 User Flash 儲存器。硬體配置包含 25MHz 石英振盪器與 ISP 在系統編程功能,搭配 Quartus II 軟體燒錄,能滿足高密度的邏輯運算與多樣化的介面橋接需求。

以上內容為 AI 生成

商品規格

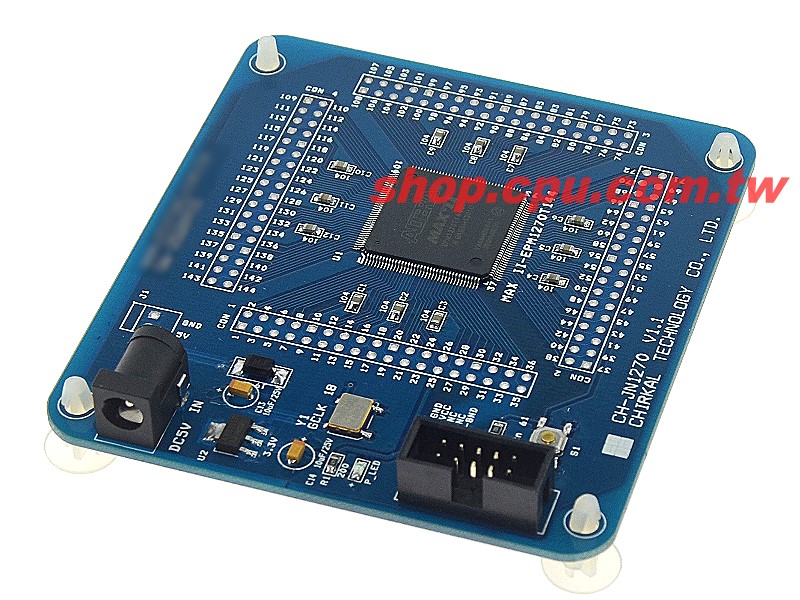

◎ 商品出廠排針已焊上,兩種型式 [ 針腳在上 ] 及 [ 針腳在下 ] 下單請備註◎ 使用ALTERA EPM1270T144C5N提供144支一般I/OPIN

◎ 提供 1個 25MHz 石英振盪器

◎ 使用 ALTERA 專用軟體Quartus II 燒錄至實驗板

◎ 提供ISP( In System Programming );需搭配ISP下載線燒錄

◎ 內建3.3V/500mA 的電壓調節器

◎ 電源供應器AC110 ~ 220 V 60Hz ; OUTPUT : 9V

商品介紹

◎ MAX II元件採用了全新的CPLD體系架構,在所有CPLD系列中單位I/O成本最低,功耗最低。◎ MAX II運用了低功耗的工藝技術,和前一代MAX元件相比,成本降低了一半,功率降至十分之一,容量增加了四倍,性能增加了兩倍。這種即用型非易失系列面向通用的小容量邏輯應用。

◎ MAX II元件除了為道統CPLD設計提供低成本方案外,還為更大容量的設計在功耗和成本上提供了改進方案,能取代更昂貴或功耗更高的FPGA、ASSP和標準邏輯器件。

◎ MAX II元件具有成本優化的體系,低功耗,用戶Flash存儲器,即時性在系統可編程(ISP),MultiVolt核心靈活性,JTAG容易使用的軟件等優點,能實現高度的功能合成,減少系統設計成本 。 在各種控制應用中如上馬達順序控制,各種系統的配置, I/O擴充和介面橋接等有著廣泛的用處。

1. CPLD元件(U1) : 為ALTERA MAX II_EPM1270T144可程式邏輯晶片。

2. 4組I/O連接排針(CON1~4): 提供使用者接於萬孔板進行實習。

3. 電源輸入端(J1) : 板上具有兩種電源連接方式,可選其中之一來作為電源輸入,其電源規格須為DC 5V,若是使用香蕉接頭作為連接時,則接頭的電源模式須為內正外負。

4. 穩壓IC(U2) : 為3.3V的穩壓IC,主要提供CPLD的工作電源與I/O的訊號位準。

5. 石英震盪器(Y1) : 作為CPLD的頻率來源,板上已規劃為第18 PIN。

6. JTAG連接座 : 可由此介面進行程式燒錄。

7. 歸復式按鍵(S1) : 可作為清除功能的指定接腳,板上已規劃為第61 PIN。

陳先生 詢問 :

您好,請問這塊版子上的IC型號是 "EPM1270T144C5" 還是 "EPM1270T144C5N"?

2012-06-27 15:18:16

廣華客服 :

目前現貨,晶片型號為 EPM1270T144C5N

2012-06-28 09:01:35

陳先生 詢問 :

請問可以另外加購下載線嗎?

2012-03-14 16:37:53

廣華客服 :

請參考

https://shop.cpu.com.tw/product/18472/info/

https://shop.cpu.com.tw/product/40718/info/

https://shop.cpu.com.tw/product/18472/info/

https://shop.cpu.com.tw/product/40718/info/

2012-03-15 09:01:55

林先生 詢問 :

請問ch-jn1270可不可以配合 FPT-1使用

2011-12-20 23:12:24

廣華客服 :

不同廠商開發的產品,應無法通用,且 FPT-1 所支援的元件為以下四種,與本產品的晶片不同,建議直接購買 FPT-1-A

● ALTERA:

EPF10K10TC144(TQFP144pin)

FPT-EPF10K10TC144

● XILINX:

XCS10TQ144(TQFP144pin)

FPT-XCS10TQ144

● ALTERA:

EPF10K10TC144(TQFP144pin)

FPT-EPF10K10TC144

● XILINX:

XCS10TQ144(TQFP144pin)

FPT-XCS10TQ144

2011-12-21 08:53:45

商品須知

- 商品因拍攝條件不同顏色可能略有差異,實際依廠商出貨為主。

- 商品情境圖為使用場景示意用,請以規格內容物為準。

- 電子零組件同一產品可能有多家供應商,每家供應商的產品尺寸可能會有差異,廣華電子商城網站上的尺寸圖『僅供參考』,請勿於收到商品前就進行 LAYOUT 或 開發。

- 產品產地不保證聲明:各廠牌製造商其製造工廠可能分佈世界各地,即使相同產品不同批號產地也可能有異,本網站上所示之產地為我司第一批進貨時產品,但不保證後續進貨產品之產地,以原廠供貨為準。

商品價格

- 電子商城非現貨產品須經由服務人員報價,請登入或註冊為本商城會員進行詢價。

- 本公司目前僅服務含台灣及其所屬離島地區,所列價格為TWD新台幣。

- 產品價格,網站可能來不及更新,所有訂單均會以電話或E-Mail確認訂單價格,未收到人員確認訂單之前請勿逕行匯款。

- 本公司盡可能維護商品規格及說明之正確性,但仍需依產品包裝或原廠公告敘述為準,本公司保留接受訂單與否的權利。

- 電子商城與公司門市價格一致,除特別註明僅限網路下單者除外。

付款

- 如使用匯款方式付款,請協助將匯款單據回傳,可縮短您訂單的處理時程。

運費

- 除特別註明之商品外,單張訂單金額未滿1400元加收運費80元,貨到付款除運費外另加收手續費50元,台灣東部及離島視情況與訂單內容需酌加收運費。

特別說明

- 所銷售的產品大部分皆屬「實驗、開發、維修或教育研究等專業用途」,供專業人士使用,非一般消費者購買後即可使用,請於購買前詳閱相關技術資料再行購買,本公司恕無法提供教學服務。

產品價格請勿在此發問,請利用聯絡我們或傳真方式詢問